ETR05066-003

## 18V Operation 500mA Synchronous Step-Down DC/DC Converters

## **■**GENERAL DESCRIPTION

The XD9263/XD9264 series are synchronous step-down DC/DC converter ICs. The XD9263/XD9264 series have operating voltage range of 3V~18V and switching frequency is 2.2 MHz and it can support 500mA as an output current with high-efficiency. Compatible with Low ESR capacitors such as ceramic capacitors for the output capacitor.

0.75V reference voltage source is incorporated in the IC, and the output voltage can be set to a value from 1.0V to 15.0V using external resistors.

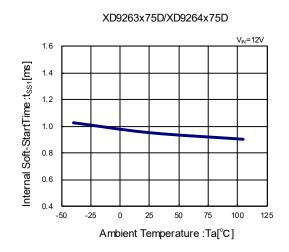

XD9263/XD9264 has a fixed internal Soft Start time which is 1.0ms (TYP.), additionally the time can be extended by using an external resistor and capacitor.

UVLO and over current protection and short-circuit protection and thermal shutdown are embedded and they secure a safety operation. As an option, timer latch off over current protection (Integral Latch Method) can be selected.

### APPLICATIONS

- Automotive Body Control ECU

- Automotive Infotainment

- Automotive accessories

- Drive recorder

- · Car-mounted camera

- ETC

- Industrial Equipment

### **■**FEATURES

**Output Capacitor**

Input Voltage Range : 3.0V ~ 18.0V (Absolute Max 20V)

Output Voltage Range 1.0V ~ 15.0V

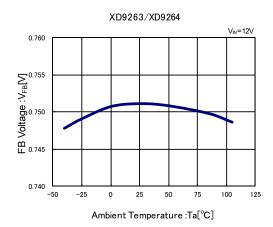

FB Voltage :  $0.75V \pm 1.5\%$  (Ta=25°C)

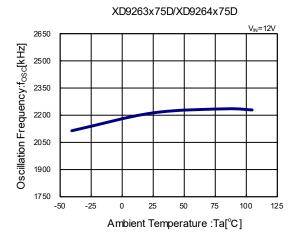

Oscillation Frequency : 2.2MHz

Output Current 500mA

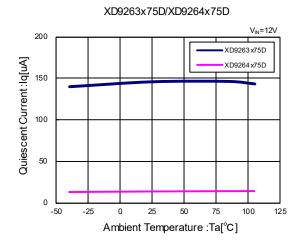

Quiescent Current : 13.5µA

Control Methods : PWM control (XD9263)

PWM/PFM Auto (XD9264)

Efficiency 85%@12V→5V, 300mA

Function : Soft-Start External settings

Power Good (USP-6C Package only)

Protect Function : Over Current Protection

Automatic Recovery (D Type)

Integral Latch Method (C Type)

UVLO

Thermal Shutdown

Ceramic Capacitor

Operating Ambient Temperature : -40°C ~ 105°C

Package : SOT-25 (Without Power Good)

USP-6C (With Power Good)

Environmentally Friendly : EU RoHS Compliant, Pb Free

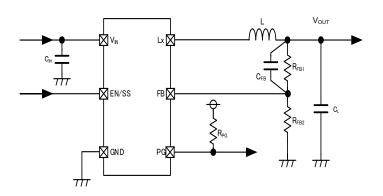

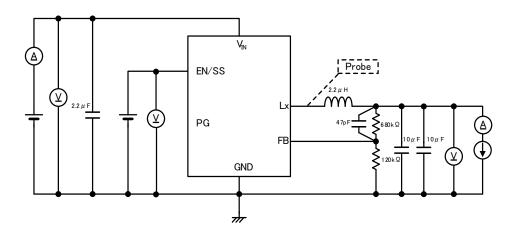

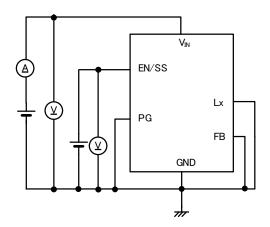

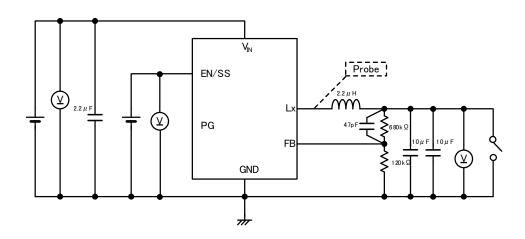

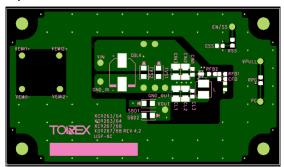

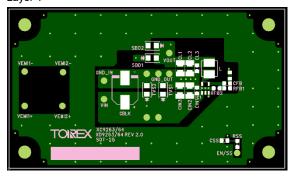

### ■TYPICAL APPLICATION CIRCUIT

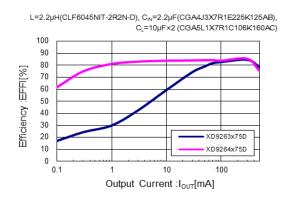

# ■TYPICAL PERFORMANCE CHARACTERISTICS

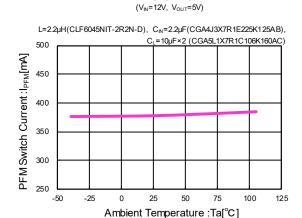

XD9263x75D/XD9264x75D $(V_{IN}=12V, V_{OUT}=5V)$

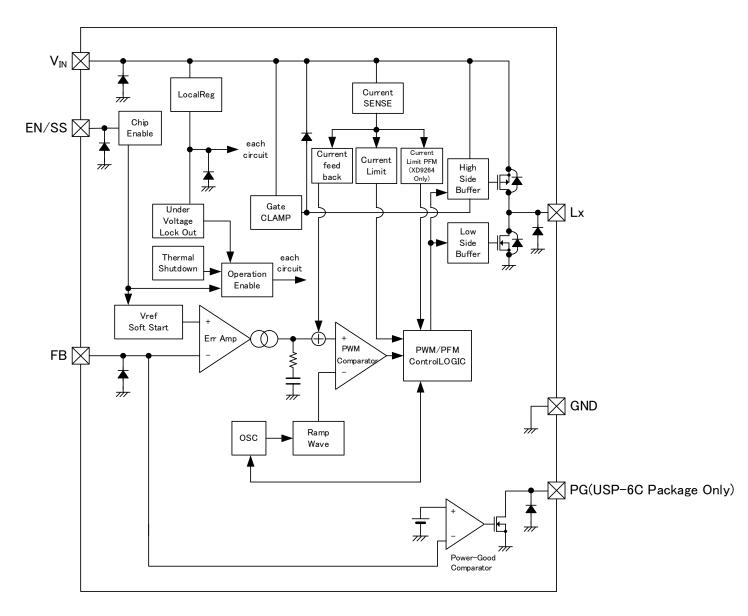

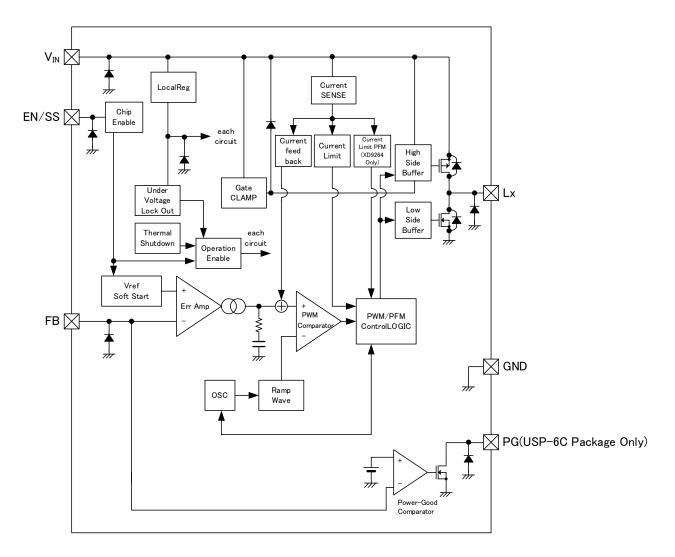

## **■BLOCK DIAGRAM**

<sup>\*</sup>Diodes inside the circuit are an ESD protection diodes and a parasitic diodes.

## **■PRODUCT CLASSIFICATION**

### Ordering Information

XD9263①2③④⑤6-⑦(\*1) PWM control XD9264①2③④⑤6-⑦(\*1) PWM/PFM Auto

| DESIGNATOR | ITEM                                            | SYMBOL    | DESCRIPTION                                 |  |  |

|------------|-------------------------------------------------|-----------|---------------------------------------------|--|--|

| ①          | Tuno                                            | С         | Refer to Selection Guide                    |  |  |

| U          | Туре                                            | D         | Refer to Selection Guide                    |  |  |

| 23         | FB Voltage 75 Output voltage can be adjusted in |           | Output voltage can be adjusted in 1V to 15V |  |  |

| 4          | Oscillation Frequency                           | D         | 2.2MHz                                      |  |  |

| \$6-7      | Packages (Order Unit)                           | MR-Q (*1) | SOT-25 (3,000pcs/Reel) (*2)                 |  |  |

|            | Packages (Order Unit)                           | ER-Q (*1) | USP-6C (3,000pcs/Reel) (*2)                 |  |  |

<sup>(\*1)</sup> The "-Q" suffix denotes "AEC-Q100" compliant.

### Selection Guide

| FUNCTION                                   | C TYPE |        | D TYPE |        |  |

|--------------------------------------------|--------|--------|--------|--------|--|

| FUNCTION                                   | SOT-25 | USP-6C | SOT-25 | USP-6C |  |

| Chip Enable                                | Yes    | Yes    | Yes    | Yes    |  |

| UVLO                                       | Yes    | Yes    | Yes    | Yes    |  |

| Thermal Shutdown                           | Yes    | Yes    | Yes    | Yes    |  |

| Soft Start                                 | Yes    | Yes    | Yes    | Yes    |  |

| Power-Good                                 | -      | Yes    | -      | Yes    |  |

| Current Limiter (Automatic Recovery)       | -      | -      | Yes    | Yes    |  |

| Current Limiter<br>(Latch Protection (*2)) | Yes    | Yes    | -      | -      |  |

<sup>(\*2)</sup> The over-current protection latch is an integral latch type.

<sup>(\*2) &</sup>quot;Halogen and Antimony free" as well as being fully EU RoHS compliant.

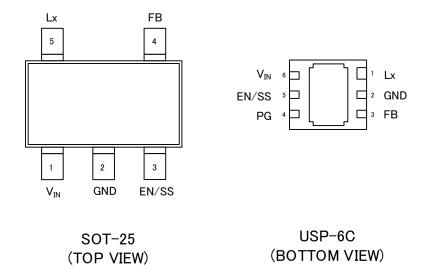

## **■PIN CONFIGURATION**

<sup>\*</sup> The dissipation pad for the USP-6C package should be solder-plated in recommended mount pattern and metal masking so as to enhance mounting strength and heat release. If the pad needs to be connected to other pins, it should be connected to the GND (No. 2) pin.

## **■ PIN ASSIGNMENT**

| PIN NU | JMBER  | PIN NAME    | FUNCTION             |

|--------|--------|-------------|----------------------|

| SOT-25 | USP-6C | PIN INAIVIE | FUNCTION             |

| 1      | 6      | Vin         | Power Input          |

| 3      | 5      | EN/SS       | Enable Soft-Start    |

| -      | 4      | PG          | Power-Good Output    |

| 4      | 3      | FB          | Output Voltage Sense |

| 2      | 2      | GND         | Ground               |

| 5      | 1      | Lx          | Switching Output     |

## **■**FUNCTION CHART

| PIN NAME | SIGNAL | STATUS              |

|----------|--------|---------------------|

|          | L      | Stand-by            |

| EN/SS    | Н      | Active              |

|          | OPEN   | Undefined State(*1) |

<sup>(\*1)</sup> Please do not leave the EN/SS pin open. Each should have a certain voltage.

| PIN NAME | CON       | SIGNAL                               |                    |

|----------|-----------|--------------------------------------|--------------------|

|          | EN/SS = H | V <sub>FB</sub> > V <sub>PGDET</sub> | H (High impedance) |

|          |           | V <sub>FB</sub> ≦ V <sub>PGDET</sub> | L (Low impedance)  |

| PG       |           | Thermal Shutdown                     | L (Low impedance)  |

|          |           | UVLO<br>(VIN < V <sub>UVLO1</sub> )  | Undefined State    |

|          | EN/SS = L | Stand-by                             | L (Low impedance)  |

## ■ ABSOLUTE MAXIMUM RATINGS

| PARAME <sup>-</sup>           | ΓER                         | SYMBOL             | RATINGS                                 | UNITS |

|-------------------------------|-----------------------------|--------------------|-----------------------------------------|-------|

| V <sub>IN</sub> Pin Vol       | V <sub>IN</sub> Pin Voltage |                    | -0.3 ~ 20                               | V     |

| EN/SS Pin V                   | oltage                      | V <sub>EN/SS</sub> | -0.3 ~ 20                               | V     |

| FB Pin Vol                    | tage                        | V <sub>FB</sub>    | -0.3 ~ 6.2                              | V     |

| PG Pin Voltage (*1)           |                             | $V_{PG}$           | -0.3 ~ 6.2                              | V     |

| PG Pin Current (*1)           |                             | I <sub>PG</sub>    | 8                                       | mA    |

| Lx Pin Vol                    | Lx Pin Voltage              |                    | -0.3 ~ V <sub>IN</sub> + 0.3 or 20 (*2) | V     |

| Lx Pin Cur                    | rent                        | I <sub>Lx</sub>    | 1800                                    | mA    |

| Power Dissipation             | SOT-25                      | Dd                 | 760 (JESD51-7 Board) <sup>(*3)</sup>    | m\\/  |

| (Ta=25°C)                     | USP-6C                      | Pd                 | 1250 (JESD51-7 Board) (*3)              | mW    |

| Operating Ambient Temperature |                             | Topr               | -40 ~ 105                               | °C    |

| Storage Temp                  | erature                     | Tstg               | -55 ~ 125                               | °C    |

$<sup>^{\</sup>ast}$  All voltages are described based on the GND pin.

<sup>(\*1)</sup> For the USP-6C Package only.

$<sup>^{(\</sup>mbox{\tiny $^{2}$})}$  The maximum value should be either  $V_{IN}\mbox{+}0.3V$  or 20V in the lowest.

<sup>(\*3)</sup> The power dissipation figure shown is PCB mounted and is for reference only. Please refer to PACKAGING INFORMATION for the mounting condition.

## **■**ELECTRICAL CHARACTERISTICS

Ta=25°C

| PARAMETER                                       | SYMBOL             |                                                                                            | CONDITIONS                                             |                | MIN.  | TYP.     | MAX.  | UNIT  | CIRCUIT  |

|-------------------------------------------------|--------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------|----------------|-------|----------|-------|-------|----------|

|                                                 |                    | V <sub>FB</sub> =0.731V → 0                                                                | 0.769V                                                 |                | 0.739 | 0.750    | 0.761 |       |          |

| FB Voltage                                      | V <sub>FB</sub>    | _                                                                                          | en Lx pin voltage<br>d" level to "L" level             | -40°C≦Ta≦105°C | 0.731 | 0.750    | 0.769 | V     | 2        |

| Output Voltage Setting<br>Range <sup>(*1)</sup> | Voutset            |                                                                                            | -                                                      | -40°C≦Ta≦105°C | 1.0   | -        | 15.0  | V     | _        |

| Operating Voltage<br>Range                      | VIN                |                                                                                            | -                                                      | -40°C≦Ta≦105°C | 3.0   | -        | 18.0  | V     | _        |

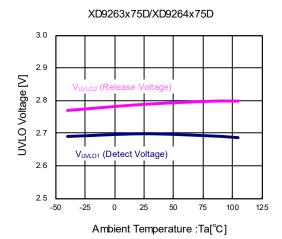

|                                                 |                    |                                                                                            | 3V, V <sub>FB</sub> =0.675V,                           |                | 2.60  | 2.70     | 2.80  |       |          |

| UVLO Detect Voltage                             | V <sub>UVLO1</sub> | V <sub>IN</sub> Voltage whe changes from "I                                                | n Lx pin voltage<br>H" level to "L" level              | -40°C≦Ta≦105°C | 2.53  | -        | 2.87  | V     | 2        |

|                                                 |                    | V <sub>IN</sub> =2.63V→2.9                                                                 |                                                        |                | 2.70  | 2.80     | 2.90  |       | _        |

| UVLO Release Voltage                            | V <sub>UVLO2</sub> | V <sub>IN</sub> Voltage whe changes from "L                                                | n Lx pin voltage<br>_" level to "H" level              | -40°C≦Ta≦105°C | 2.63  | -        | 2.97  | V     | 2        |

|                                                 |                    | XD9263                                                                                     |                                                        | -              | 145   | 238      |       |       |          |

| Quiescent Current                               | $I_q$              | V <sub>FB</sub> =0.825V                                                                    | AB3200                                                 | -40°C≦Ta≦105°C | -     | -        | 257   | μA    | 4        |

| Quiossoni Guironi                               | •4                 | XD9264                                                                                     | XD9264                                                 | Γ              | -     | 13.5     | 18.5  | μΛ    |          |

|                                                 |                    |                                                                                            | 7,50201                                                | -40°C≦Ta≦105°C | -     | -        | 20.0  |       |          |

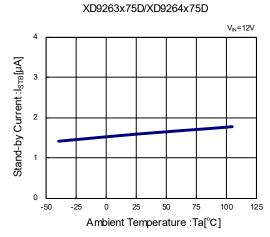

| Stand-by Current                                | I <sub>STB</sub>   | V <sub>EN/SS</sub> =0V                                                                     |                                                        |                | -     | 1.65     | 2.50  | μA    | (5)      |

|                                                 | 1015               | ·                                                                                          |                                                        | -40°C≦Ta≦105°C | -     | -        | 2.80  | μ" .  |          |

| 0 11 11 5                                       | ,                  | Connected to ex                                                                            | rternal                                                |                | 2013  | 2200     | 2387  | 1.11= |          |

| Oscillation Frequency                           | fosc               | components<br>I <sub>OUT</sub> =100mA                                                      |                                                        | -40°C≦Ta≦105°C | 1813  | -        | 2531  | kHz   | 1        |

| Minimum Duty Cycle                              | $D_{MIN}$          | V <sub>FB</sub> =0.825V                                                                    |                                                        | -40°C≦Ta≦105°C | -     | -        | 0     | %     | 2        |

| Maximum Duty Cycle                              | D <sub>MAX</sub>   | V <sub>FB</sub> =0.675V                                                                    |                                                        | -40°C≦Ta≦105°C | 100   | -        | -     | %     | 2        |

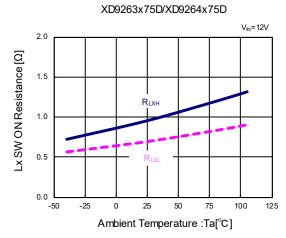

| Lx SW "H" On                                    | Б                  | \/ -0.675\/ L -                                                                            | -200 A                                                 | USP-6C         | -     | 0.95     | 1.10  | _     | <u> </u> |

| Resistance                                      | $R_{LxH}$          | V <sub>FB</sub> =0.675V, I <sub>LX</sub> =                                                 | -200MA                                                 | SOT-25         | -     | 0.99     | 1.14  | Ω     | 2        |

| Lx SW "L" On                                    |                    | \/ -0.00E\/                                                                                | -200 m A                                               | USP-6C         | -     | 0.69(*2) | -     |       | <u></u>  |

| Resistance                                      | $R_{LxL}$          | V <sub>FB</sub> =0.825V, I <sub>LX</sub> =                                                 | -200MA                                                 | SOT-25         | -     | 0.73(*2) | -     | Ω     | 2        |

| PFM Switch Current                              | <b>I</b> PFM       | XD9264 only<br>Connected to ex                                                             | XD9264 only Connected to external components, IouT=1mA |                | -     | 370      | -     | mA    | 1        |

| Highside Current<br>Limit <sup>(*3)</sup>       | I <sub>LIMH</sub>  | V <sub>FB</sub> =0.675V                                                                    |                                                        | 920            | 1100  | -        | mA    | 2     |          |

| Latch Time                                      | t <sub>LAT</sub>   | Type C only Connected to external components, V <sub>FB</sub> =0V                          |                                                        | 0.5            | 1.0   | 1.7      | ms    | 6     |          |

| Internal Soft-Start Time                        | tss1               | V <sub>EN/SS</sub> =0V→12V, V <sub>FB</sub> =0.675V<br>Time until Lx pin oscillates        |                                                        |                | 0.5   | 1.0      | 1.7   | ms    | 2        |

| External Soft-Start Time                        | tss2               | V <sub>EN/SS</sub> =0V→12V<br>R <sub>SS</sub> =430kΩ, C <sub>SS</sub><br>Time until Lx pir | /, V <sub>FB</sub> =0.675V<br><sub>S</sub> =0.47μF     |                | 17    | 26       | 35    | ms    | 3        |

Test Condition: Unless otherwise stated, V<sub>IN</sub>=12V, V<sub>EN/SS</sub>=12V.

The ambient temperature range (-40°C  $\leq$  Ta  $\leq$  105°C) is design Value.

$<sup>^{(^{\</sup>star}1)}$  Please use within the range of  $V_{\text{OUT}}/V_{\text{IN}}{\geqq}0.17.$

<sup>(\*2)</sup> Design reference value. This parameter is provided only for reference.

<sup>(\*3)</sup> Current limit denotes the level of detection at peak of coil current.

# ■ ELECTRICAL CHARACTERISTICS (Continued)

Ta=25°C

| PARAMETER                    | SYMBOL              | CONDITIONS                                                                                                                                             |                | MIN.  | TYP.   | MAX.  | UNIT     | CIRCUIT |

|------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------|--------|-------|----------|---------|

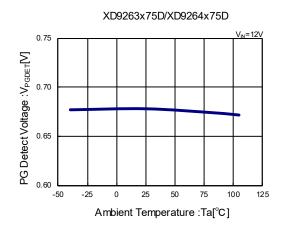

| PG Detect Voltage(*4)        | $V_{PGDET}$         | $V_{FB}$ =0.720 $V$ $\rightarrow$ 0.630 $V$ ,<br>R <sub>PG</sub> :100k $\Omega$ pull-up to 5 $V$                                                       |                | 0.638 | 0.675  | 0.712 | V        | 2       |

| 1 & Beleet Vollage           | VPGDET              | V <sub>FB</sub> Voltage when PG pin voltage changes from "H" level to "L" level                                                                        | -40°C≦Ta≦105°C | 0.630 | -      | 0.720 |          |         |

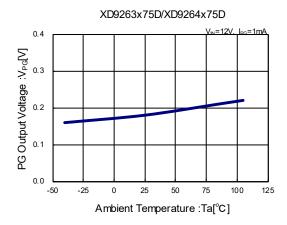

| PG Output Voltage(*4)        | $V_{PG}$            | V <sub>FB</sub> =0.6V, I <sub>PG</sub> =1mA                                                                                                            | -40°C≦Ta≦105°C | -     | -      | 0.3   | V        | 2       |

| Efficiency                   | EFFI (*5)           | Connected to external components Voutset=5V, Iout=300mA                                                                                                | 3              | -     | 85(*2) | ı     | %        | 1       |

| FB "H" Current               | І <sub>ГВН</sub>    | V <sub>IN</sub> =V <sub>EN/SS</sub> =18V,<br>V <sub>FB</sub> =3.0V                                                                                     | -40°C≦Ta≦105°C | -0.1  | 0.0    | 0.1   | μΑ       | 4       |

| FB "L" Current               | I <sub>FBL</sub>    | V <sub>IN</sub> =V <sub>EN/SS</sub> =18V,<br>V <sub>FB</sub> =0V                                                                                       | -40°C≦Ta≦105°C | -0.1  | 0.0    | 0.1   | μΑ       | 4       |

| EN/SS "H" Current            | I <sub>EN/SSH</sub> | V <sub>IN</sub> =V <sub>EN/SS</sub> =18V,<br>V <sub>FB</sub> =0.825V                                                                                   | -40°C≦Ta≦105°C | -     | 0.1    | 0.3   | μΑ       | 4       |

| EN/SS "L" Current            | I <sub>EN/SSL</sub> | V <sub>IN</sub> =18V, V <sub>EN/SS</sub> =0V,<br>V <sub>FB</sub> =0.825V                                                                               | -40°C≦Ta≦105°C | -0.1  | 0.0    | 0.1   | μΑ       | 4       |

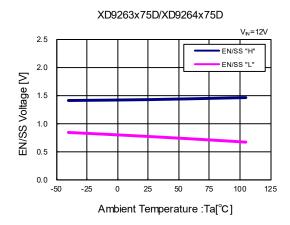

| EN/SS "H" Voltage            | V <sub>EN/SSH</sub> | V <sub>EN/SS</sub> =0.3V→2.5V, V <sub>FB</sub> =0.71V<br>V <sub>EN/SS</sub> Voltage when Lx pin voltage<br>changes from "L" level to "H" level         |                | 2.5   | ı      | 18.0  | >        | 2       |

| EN/SS "L" Voltage            | V <sub>EN/SSL</sub> | $V_{\text{EN/SS}}$ =2.5V $\rightarrow$ 0.3V, $V_{\text{FB}}$ =0.71V $V_{\text{EN/SS}}$ Voltage when Lx pin voltage changes from "H" level to "L" level |                | GND   | ı      | 0.3   | <b>V</b> | 2       |

| Thermal Shutdown Temperature | T <sub>TSD</sub>    | Junction Temperature                                                                                                                                   |                | -     | 150    | -     | °C       | -       |

| Hysteresis Width             | T <sub>HYS</sub>    | Junction Temperature                                                                                                                                   |                | -     | 25     | -     | ့        | _       |

Test Condition: Unless otherwise stated, V<sub>IN</sub>=12V, V<sub>EN/SS</sub>=12V.

The ambient temperature range (-40°C≦Ta≦105°C) is design Value.

<sup>(\*1)</sup> Please use within the range of V<sub>OUT</sub>/V<sub>IN</sub>≥0.17/

<sup>(\*2)</sup> Design reference value. This parameter is provided only for reference.

<sup>(\*3)</sup> Current limit denotes the level of detection at peak of coil current.

<sup>(\*4)</sup> For the USP-6C Package only.

<sup>(\*5)</sup> EFFI = {(output voltage) x (output current)} / {(input voltage) x (input current)} x 100

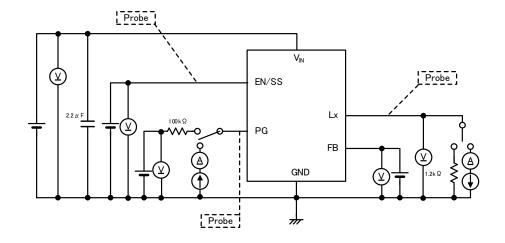

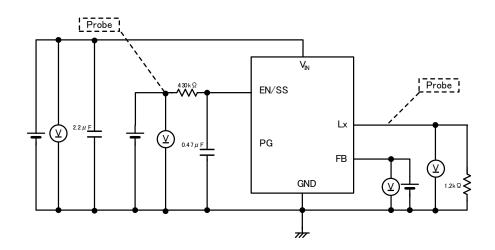

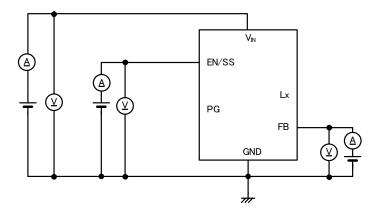

## ■TEST CIRCUITS

### CIRCUIT(1)

### CIRCUIT②

## CIRCUIT®

<sup>\*</sup> PG Pin is USP-6C Package only.

# ■TEST CIRCUITS (Continued)

## CIRCUIT4

### CIRCUIT®

## CIRCUIT®

<sup>\*</sup> PG Pin is USP-6C Package only.

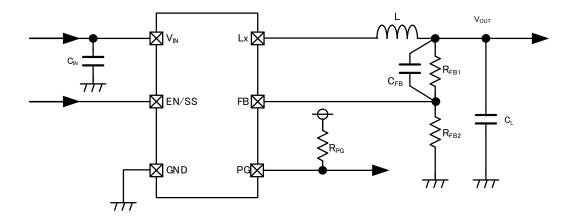

## ■TYPICAL APPLICATION CIRCUIT / PARTS SELECTION METHOD

### [Typical Examples]

|                      | MANUFACTURER | PRODUCT NUMBER       | VALUE              |

|----------------------|--------------|----------------------|--------------------|

| L                    | TDK          | CLF6045NIT-2R2N-D    | 2.2µH              |

| C <sub>IN</sub> (*1) | TDK          | CGA4J3X7R1E225K125AB | 2.2µF/25V          |

|                      | Murata       | GRT21BR71A106KE13    | 10μF/10V 2parallel |

| C <sub>L</sub> (*2)  | TDK          | CGA5L1X7R1C106K160AC | 10μF/16V 2parallel |

|                      | Murata       | GRT32DC81E106KE01    | 10μF/25V 2parallel |

Select parts considering the DC bias characteristics and rated voltage of ceramic capacitors.

<sup>(\*1)</sup> For C<sub>IN</sub>, use a capacitor with the same or higher effective capacity value as the recommended components.

<sup>(\*2)</sup> For C<sub>L</sub>, use a capacitor with the same or higher effective capacity value as the recommended components. If a capacitor with a low effective capacity value is used, the output voltage may become unstable. However, if large capacity capacitors, such as electrolytic capacitors, are connected in parallel, the inrush current during startup could increase or the output could become unstable.

## ■TYPICAL APPLICATION CIRCUIT / PARTS SELECTION METHOD

<Output voltage setting Value Voutset Setting >

The output voltage can be set by adding an external dividing resistor.

The output voltage is determined by the equation below based on the values of  $R_{FB1}$  and  $R_{FB2}$ .

$$V_{OUT}$$

= $V_{FB}$ × $(R_{FB1}$ + $R_{FB2}$ )/ $R_{FB2}$

With  $R_{FB1}$ + $R_{FB2}$  $\leq 1M\Omega$

<C<sub>FB</sub> setting>

Adjust the value of the phase compensation speed-up capacitor CFB using the equation below.

$$C_{FB} = \frac{1}{2\pi \times fz fb \times R_{FB1}}$$

\* A target value for fzfb of about 5kHz is optimum.

[Output voltage Setting Example]

To set output voltage to 5V.

When R<sub>FB1</sub>=680k $\Omega$ , R<sub>FB2</sub>=120k $\Omega$ , V<sub>OUTSET</sub>=0.75V×(680k $\Omega$ +120k $\Omega$ ) / 120k $\Omega$ =5.0V, and fzfb is set to a target of 5kHz using the above equation, C<sub>FB</sub>=1/(2× $\pi$ ×5kHz×680k $\Omega$ )=46.8pF.

\* The setting range for the output voltage is 1.0V to 15.0V.

The condition  $V_{\text{OUT}}\!/\!V_{\text{IN}} \geqq 0.17$  must be satisfied.

### [Setting Example]

| Voutset | R <sub>FB1</sub> [kΩ] | R <sub>FB2</sub> [kΩ] | C <sub>FB</sub> [pF] |

|---------|-----------------------|-----------------------|----------------------|

| 1.2     | 91                    | 150                   | 360                  |

| 3.3     | 510                   | 150                   | 62                   |

| 5.0     | 680                   | 120                   | 47                   |

| 12      | 360                   | 24                    | 91                   |

## **■**OPERATIONAL EXPLANATION

The XD9263/XD9264 series consist internally of a reference voltage supply with Soft Start function, a ramp wave circuit, an error amp, a PWM comparator, a High side driver FET, a Low side driver FET, a High side buffer circuit, a Low side buffer circuit, a current sense circuit, a phase compensation (Current feedback) circuit, a current limiting circuit, an under voltage lockout (UVLO) circuit, an internal power supply (Local Reg) circuit, a gate clamp (CLAMP) circuit and other elements.

The control method is the current mode control method for handling low ESR ceramic capacitors.

\*Diodes inside the circuit are ESD protection diodes and parasitic diodes.

## ■ OPERATIONAL EXPLANATION(Continued)

### < Normal Operation >

The standard voltage Vref and FB pin voltage are compared using an error amplifier and then the control signal to which phase compensation has been added to the error amplifier output is input to the PWM comparator. The PWM comparator compares the above control signal and lamp wave to control the duty width during PWM control. Continuously conducting these controls stabilizes the output voltage.

In addition, the current detecting circuit monitors the driver FET current for each switching and modulates the error amplifier output signal into a multiple feedback signal (current feedback circuit). This achieves stable feedback control even when low ESR capacitors, such as ceramic capacitors, are used to stabilize the output voltage.

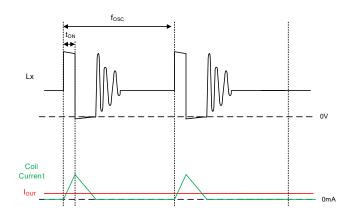

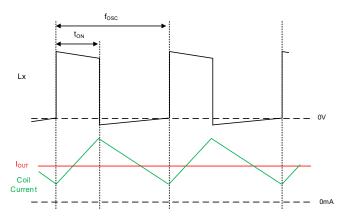

### XD9263 Series

The XD9263 Series (PWM control) performs switching at a set switching frequency fosc regardless of the output current. At light loads the on time is short and the circuit operates in discontinuous mode, and as the output current increases, the on time becomes longer and the circuit operates in continuous mode.

XD9263 Series: Example of light load operation

XD9263 Series: Example of heavy load operation

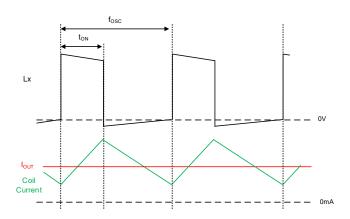

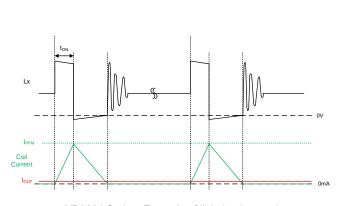

### XD9264 Series

The XD9264 Series (PWM/PFM automatic switching control) lowers the switching frequency during light loads by turning on the High side driver FET when the coil current reaches the PFM current (I<sub>PFM</sub>). This operation reduces the loss during light loads and achieves high efficiency from light to heavy loads. As the output current increases, the switching frequency increases proportional to the output current, and when the switching frequency increases fosc, the circuit switches from PFM control to PWM control and the switching frequency becomes fixed.

XD9264 Series: Example of heavy load operation

### < 100% Duty Cycle Mode >

When the dropout voltage is low or there is a transient response, the circuit might change to the 100% Duty cycle mode where the High side driver FET is continuously on.

The 100% Duty cycle mode operation makes it possible to maintain the output current even when the dropout voltage is low such as when the input voltage declines due to cranking, etc.

## ■ OPERATIONAL EXPLANATION(Continued)

### < CE Function >

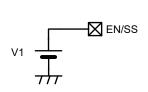

When an "H" voltage ( $V_{EN/SSH}$ ) is input to the EN/SS pin, normal operation is performed after the output voltage is started up by the Soft Start function, normal operation is performed. When the "L" voltage ( $V_{EN/SSL}$ ) is input to the EN/SS pin, the circuit enters the standby state, the supply current is suppressed to the standby current  $I_{STB}$  (TYP. 1.65 $\mu$ A), and the High side driver FET and Low side driver FET are turned off.

### < Soft Start Function >

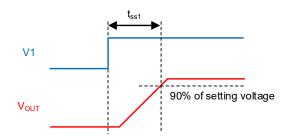

This function gradually starts up the output voltage to suppress the inrush current.

The Soft Start time is the time until the output voltage from V<sub>EN/SSH</sub> reaches 90% of the output voltage set value, and when the output voltage increases further, the Soft Start function is cancelled to switch to normal operation.

### **Internal Soft Start Time**

The internal Soft Start time (tss1) is configured so that after the "H" voltage (VEN/SSH) is input to the EN/SS pin, the standard voltage connected to the error amplifier increases linearly during the Soft Start period. This causes the output voltage to increase proportionally to the standard voltage increase. This operation suppresses the inrush current and smoothly increases the output voltage.

< Internal Soft Start EN/SS circuit >

< Overview of internal Soft Start >

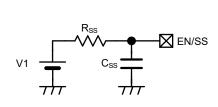

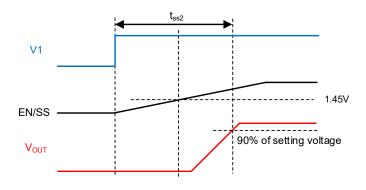

### **External Setting Soft Start Time**

The external setting Soft Start time ( $t_{SS2}$ ) can adjust the increase speed of the standard voltage in the IC by adjusting the EN/SS pin voltage inclination during startup using externally connected component  $R_{SS}$  and  $C_{SS}$ . This makes it possible to externally adjust the Soft Start time.

Soft Start time ( $t_{SS2}$ ) is approximated by the equation below according to values of V1, R<sub>SS</sub>, and C<sub>SS</sub>. When  $t_{ss2}$  is shorter than  $t_{ss1}$ , the output voltage rises at the internal Soft Start time.

### [Setting Example]

$C_{SS} = 0.47 \mu F$ ,  $R_{SS} = 430 k\Omega$ , V1 = 12 V

$t_{SS2} = 0.47 \mu F \times 430 k\Omega \times (ln (12V/(12V-1.45V)) = 26ms$

< External Soft Start EN/SS circuit >

< Overview of external Soft Start >

## ■ OPERATIONAL EXPLANATION (Continued)

### < Power Good >

The output state can be monitored using the power good function. The PG pin is an Nch open drain output, therefore a pull-up resistor (approx.  $100k\Omega$ ) must be connected to the PG pin.

The pull-up voltage should be 5.5V or less. When not using the power good function, connect the PG terminal to GND or leave it open.

| CONDI      | SIGNAL                               |                    |

|------------|--------------------------------------|--------------------|

|            | V <sub>FB</sub> > V <sub>PGDET</sub> | H (High impedance) |

| EN/SS = H  | $V_{FB} \leq V_{PGDET}$              | L (Low impedance)  |

| EN/33 - FI | Thermal Shutdown                     | L (Low impedance)  |

|            | UVLO (VIN < VUVLOD)                  | Undefined State    |

| EN/SS = L  | Stand-by                             | L (Low impedance)  |

### <UVLO>

This is a function to monitor the internal power supply and to prevent the output of false pulses from the Lx pin when the output from the internal power supply is unstable at low voltages. As the  $V_{IN}$  pin voltage goes down, the internal power supply voltage falls. So the  $V_{IN}$  voltage drops, the UVLO function is activated.

When the  $V_{IN}$  pin voltage falls below  $V_{UVLO1}$  (TYP. 2.7V), the UVLO function is activated, the high side driver FET and low side driver FET are forcibly turned off to prevent false pulse output due to instable operation of the internal circuits. When the  $V_{IN}$  pin voltage rises above  $V_{UVLO2}$  (TYP. 2.8V), the UVLO function is released, the soft start function activates, and output start operation begins. Stopping by UVLO is not shutdown; only pulse output is stopped and the internal circuits continue to operate.

### < Thermal Shutdown Function >

A thermal shutdown (TSD) function is built in for protection from overheating. When the junction temperature reaches the thermal shutdown detection temperature  $T_{TSD}$ , the High side driver FET and Low side driver FET are compulsorily turned off.

If the driver FET continues in the off state, the junction temperature declines, and when the junction temperature falls to the thermal shutdown cancel temperature, the thermal shutdown function is cancelled and the Soft Start function operates to start up the output voltage.

# XD9263/XD9264 Series

## ■ OPERATIONAL EXPLANATION (Continued)

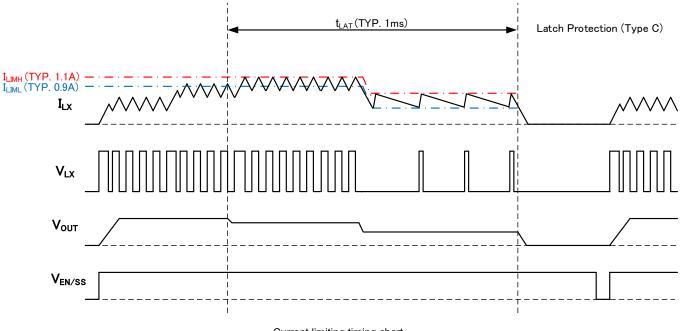

### <Current limiting>

The current limiting circuit of the XD9263/XD9264 series monitor the current that flows through the High side driver transistor and Low side driver transistor, and when over-current is detected, the current limiting function activates.

### 1 High side driver Tr. current limiting

The current in the High side driver Tr. is detected to equivalently monitor the peak value of the coil current. The High side driver Tr. current limiting function forcibly turns off the High side driver Tr. when the peak value of the coil current reaches the High side driver current limit value ILIMH.

High side driver Tr. current limit value I<sub>LIMH</sub>=1.1A (TYP.)

### 2 Low side driver Tr. current limiting

The current in the Low side driver Tr. is detected to equivalently monitor the bottom value of the coil current. The Low side driver Tr. current limiting function operates when the High side driver Tr. current limiting value reaches I<sub>LIMH</sub>. The Low side driver Tr. current limiting function prohibits the High side driver Tr. from turning on in an over current state where the bottom value of the coil current is higher than the Low side driver Tr. current limit value I<sub>LIML</sub>.

Low side driver Tr. current limit value ILIML=0.9A (TYP.)

When the output current increases and reaches the current limit value, the current foldback circuit operates and lowers the output voltage and FB voltage. The ILIMH and ILIML decline accompanying the FB voltage decrease to restrict the output current.

When the overcurrent state is removed, the foldback circuit operation increases the  $I_{LIMH}$  and  $I_{LIML}$  together with output voltage to return the output to the output voltage set value.

### ③ Over current latch (Type C)

Type C turns off the High side and Low side driver Tr. when state 1 or 2 continues for  $t_{LAT}$  (TYP. 1.0ms). The L<sub>X</sub> pin is latch stopped at the GND level (0V).

The latch stopped state only stops the pulse output from the Lx pin; the internal circuitry of the IC continues to operate. To restart after latch stopping, L level and then H level must be input into the EN/SS pin, or  $V_{IN}$  pin re-input must be performed (after lowering the voltage below the UVLO detection voltage) to resume operation by Soft-Start.

The over current latch function may occasionally be released from the current limit detection state by the effects of ambient noise, and it may also happen that the latch time becomes longer or latching does not take place due to board conditions. For this reason, place the input capacitor as close as possible to the IC.

Type D is an automatic recovery type that performs the operation of ① or ② until the over current state is released.

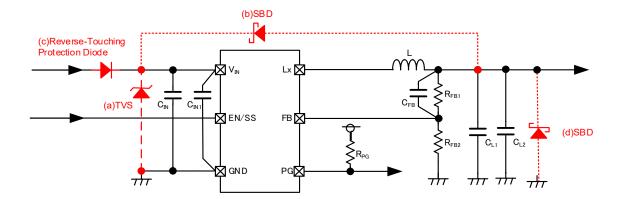

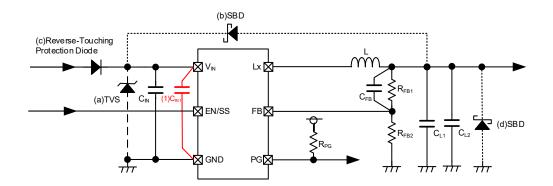

## **■**NOTES ON USE

In the case of a temporary and transient voltage drop or voltage rise.

If the absolute maximum ratings are exceeded, the IC may be deteriorate or destroyed.

If a voltage exceeding the absolute maximum voltage is applied to the IC due to chattering caused by a mechanical switch or an external surge voltage, please use a protection element such as a TVS and a protection circuit as a countermeasure. Please see the countermeasures from (a) to (d) shown below.

(a) When voltage exceeding the absolute maximum ratings comes into the  $V_{IN}$  pin due to the transient change on the power line, there is a possibility that the IC breaks down in the end.

To prevent such a failure, please add a TVS between V<sub>IN</sub> and GND as a countermeasure.

(b) When the input voltage decreases below the output voltage, there is a possibility that an overcurrent will flow in the IC's Internal parasitic diode and exceed the absolute maximum rating of the Lx pin.

If the current is pulled into the input side by the low impedance between  $V_{IN}$  and GND, then countermeasures, such as adding an SBD between  $V_{OUT}$  and  $V_{IN}$ , should be taken.

- (c) When a negative voltage is applied to the input voltage by a reverse connection or chattering, an overcurrent could flow in the IC's parasitic diode and damage the IC. Take countermeasures, such as adding a reverse touching protection diode.

- (d) When a sudden surge of electrical current travels along the  $V_{\text{OUT}}$  pin and GND due to a short-circuit, electrical resonance of a circuit involving parasitic inductor of cable related to short circuit and an output capacitor ( $C_L$ ) and impedance such as  $V_{\text{OUT}}$  line generates a negative voltage exceeding the breakdown voltage and may damage the device. Take countermeasures, such as connecting a schottky diode between the  $V_{\text{OUT}}$  and GND.

# XD9263/XD9264 Series

## ■NOTES ON USE(Continued)

- 2) Make sure that the absolute maximum ratings of the external components and of this IC are not exceeded.

- 3) The DC/DC converter characteristics depend greatly on the externally connected components as well as on the characteristics of this IC, so refer to the specifications and standard circuit examples of each component when carefully considering which components to select.

- Be especially careful of the capacitor characteristics and use X7R or X5R (EIA standards) ceramic capacitors.

- The capacitance decrease caused by the bias voltage may become large depending on the external size of the capacitor.

- 4) The current limit value is the coil current peak value when switching is not conducted. The coil current peak value when the actual current limit function begins to operate may exceed the current limit of the electrical characteristics due to the effect of the propagation delay inside the circuit.

- 5) When the On time is less than the Minimum On Time (tonmin) and the dropout voltage is large or the load is low, the PWM control operates intermittently and the Vout ripple voltage may become large or the output voltage may become unstable.

- 6) The V<sub>OUT</sub> ripple voltage could be increased when switching from discontinuous conduction mode to continuous conduction mode and when switching to 100% Duty cycle.

- 7) The PWM/PFM auto series may cause superimposed V<sub>OUT</sub> ripple voltage by continuous pulses if used in high temperature and no load conditions. It is necessary to set an idle current of higher than 100µA from V<sub>OUT</sub> if used at no load. It can have the same effect as when R<sub>FB2</sub> is lower than 7.5kΩ. Please refer to the < Output Voltage Setting Value V<sub>OUTSET</sub> Setting > section under TYPICAL APPLICATION CIRCUIT.

- 8) If the voltage at the EN/SS Pin does not start from 0V but it is at the midpoint potential when the power is switched on, the Soft Start function may not work properly and it may cause larger inrush current and bigger V<sub>OUT</sub> ripple voltages.

- 9) The effects of ambient noise and the state of the circuit board may cause release from the current limiting state, and the latch time may lengthen or latch operation may not take place. Please evaluate IC well on customer's PCB.

- 10) Torex places an importance on improving our products and their reliability. We request that users incorporate fail safe designs and post aging protection treatment when using Torex products in their systems.

- 11) In order to drive the IC normally, supply a stable input voltage to the V<sub>IN</sub> pin after reducing the AC impedance due to the bypass capacitor. In particular, if the amplitude of the input voltage fluctuates by 2V or more and ±0.1V/µs or more, there is a possibility that the UVLO function malfunctions due to fluctuations of the internal power supply of the IC. In that case, switching is stopped in a protected state that prevents false pulse output from the Lx pin. After that, the soft start function gets started, it shifts to normal operation.

- If the input voltage fluctuates momentarily, take measures such as increasing the input capacitance.

## ■NOTES ON USE(Continued)

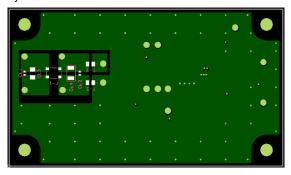

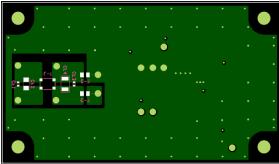

### 12) Instructions of pattern layouts.

The operation may become unstable due to noise and/or phase lag from the output current when the wire impedance is high, please place the input capacitor( $C_{IN}$ ) and the output capacitor ( $C_L$ ) as close to the IC as possible.

(1) In order to stabilize V<sub>IN</sub> voltage level, we recommend that a by-pass capacitor (C<sub>IN1</sub>) be connected as close as possible to the V<sub>IN</sub> and GND pins. If fluctuation of the VIN potential is expected, please take measures such as increasing input capacitor(C<sub>IN</sub>).

- (2) Please mount each external component as close to the IC as possible.

Please place the external parts on the same side of the PCB as the IC, not on the reverse side of the PCB and elsewhere.

- (3) Wire external components as close to the IC as possible and use thick, short connecting traces to reduce the circuit impedance.

- (4) Make sure that the GND traces are as thick as possible, as variations in ground potential caused by high ground currents at the time of switching may result in instability of the IC.

- (5) This product has a built in driver FET, which causes heat generation from the on resistance, so take measures to dissipate the heat when necessary.

# ■NOTE ON USE (Continued)

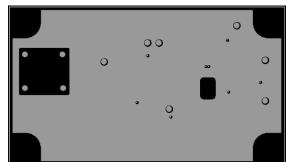

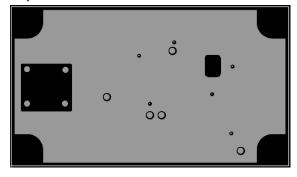

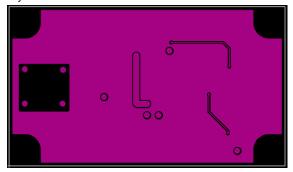

<Reference Pattern Layout>

### ●USP-6C

Layer 1

Layer 2

Layer 3

Layer 4

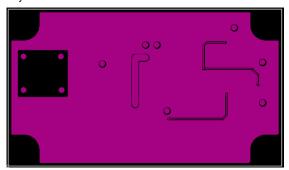

### ●SOT-25

Layer 1

Layer 2

Layer 3

Layer 4

## **■**TYPICAL PERFORMANCE CHARACTERISTICS

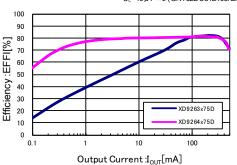

### (1) Efficiency vs. Output current

#### XD9263x75D/XD9264x75D (V<sub>IN</sub>=12V, V<sub>OUT</sub>=3.3V)

L=2.2  $\mu$  H(CLF6045NIT-2R2),  $C_N$ =2.2  $\mu$  F(GRT31CC81H225KE01),  $C_L$ =10  $\mu$  F × 2 (GRT32DC81E106KE01)

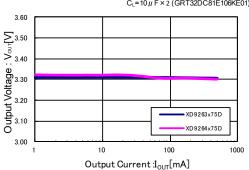

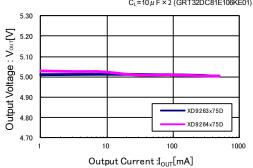

### (2) Output Voltage vs. Output Current

#### XD9263x75D/XD9264x75D $(V_{IN}=12V, V_{OUT}=3.3V)$

L=2.2  $\mu$  H(CLF6045NIT-2R2),  $C_{\rm IN}$ =2.2  $\mu$  F(GRT31CC81H225KE01),  $C_{\rm L}$ =10  $\mu$  F × 2 (GRT32DC81E106KE01)

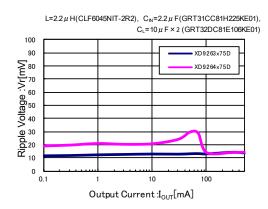

### (3) Ripple Voltage vs. Output Current

### XD9263x75D/XD9264x75D (V<sub>IN</sub>=12V, V<sub>OUT</sub>=5V)

#### XD9263x75D/XD9264x75D $(V_N=12V, V_{OUT}=5V)$

L=2.2µH(CLF6045NIT-2R2), CIN=2.2µF(GRT31CC81H225KE01), CI =10uF×2 (GRT32DC81F106KE01)

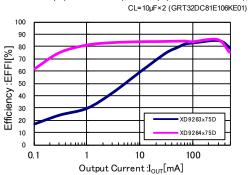

### XD9263x75D/XD9264x75D

$(V_{IN}=12V, V_{OUT}=5V)$

L=2.2  $\mu$  H(CLF6045NIT-2R2),  $C_N$ =2.2  $\mu$  F(GRT31CC81H225KE01),  $C_L$ =10  $\mu$  F × 2 (GRT32DC81E106KE01)

### (4) FB Voltage vs. Ambient Temperature

(5) UVLO Voltage vs. Ambient Temperature

(7) Stand-by Current vs. Ambient Temperature

(9) Quiescent Current vs. Ambient Temperature

(6) Oscillation Frequency vs. Ambient Temperature

(8) Lx SW ON Resistance vs. Ambient Temperature

(10) Internal Soft-Start Time vs. Ambient Temperature

### (11) External Soft-Start Time vs. Ambient Temperature

#

50

Ambient Temperature :Ta[°C]

100

125

XD9263x75D/XD9264x75D

# (12) PFM Switch Current vs. Ambient Temperature XD9264x75D

### (13) PG Detect Voltage vs. Ambient Temperature

-50

### (14) PG Output Voltage vs. Ambient Temperature

### (15) EN/SS Voltage vs. Ambient Temperature

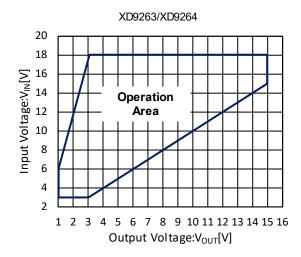

### (16) V<sub>IN</sub>-V<sub>OUT</sub> Operation Area

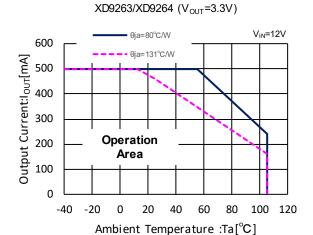

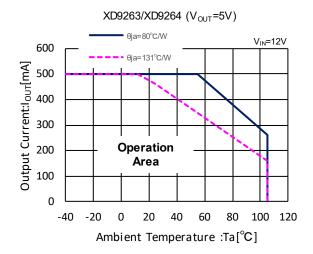

### (17) Output Current Operation Area

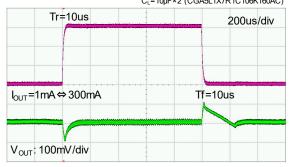

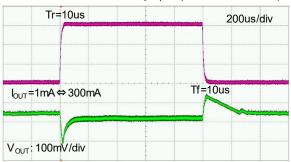

### (18) Load Transient Response

### XD9263x75D

V<sub>IN</sub>=12V, V<sub>OUT</sub>=5.0V, I<sub>OUT</sub>=1mA⇔300mA

L=2.2µH(CLF6045NIT-2R2N-D), C<sub>N</sub>=2.2µF(CGA4J3X7R1E225K125AB), C<sub>I</sub>=10µF×2 (CGA5L1X7R1C106K160AC)

### XD9264x75D

V<sub>IN</sub>=12V, V<sub>OUT</sub>=5.0V, I<sub>OUT</sub>=1mA⇔300mA

L=2.2 $\mu$ H(CLF6045NIT-2R2N-D), C<sub>N</sub>=2.2 $\mu$ F(CGA4J3X7R1E225K125AB), C<sub>L</sub>=10 $\mu$ F×2 (CGA5L1X7R1C106K160AC)

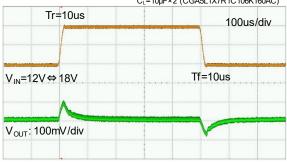

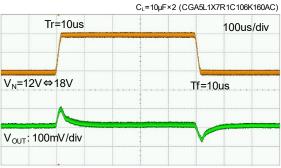

### (19) Input Transient Response

### XD9263x75D

$V_{IN}$ =12V $\Leftrightarrow$ 18V,  $V_{OUT}$ =5V,  $I_{OUT}$ =300mA

$\label{eq:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma:lemma$

### XD9264x75D

$V_{IN}$ =12V $\Leftrightarrow$ 18V,  $V_{OUT}$ =5V,  $I_{OUT}$ =300mA

L=2.2µH(CLF6045NIT-2R2N-D), C<sub>N</sub>=2.2µF(CGA4J3X7R1E225K125AB),

### (20) EN/SS Rising Response

### XD9263x75D

$V_{IN}$ =12V,  $V_{EN/SS}$ =0V $\rightarrow$ 12V,  $V_{OUT}$ =5V,  $I_{OUT}$ =300mA

$\label{eq:local_local} $$L=2.2\mu H(CLF6045NIT-2R2N-D), $$C_N=2.2\mu F(CGA4J3X7R1E225K125AB),$$$C_L=10\mu F\times 2$$(CGA5L1X7R1C106K160AC)$$$

### XD9264x75D

$V_{IN}$ =12V,  $V_{EN/SS}$ =0V $\rightarrow$ 12V,  $V_{OUT}$ =5V,  $I_{OUT}$ =300mA

$L=2.2 \mu H (CLF6045NIT-2R2N-D), \quad C_N=2.2 \mu F (CGA4J3X7R1E225K125AB), \\ C_L=10 \mu F\times 2 \ (CGA5L1X7R1C106K160AC)$

## **■**PACKAGING INFORMATION

For the latest package information go to, <a href="www.torexsemi.com/technical-support/packages/">www.torexsemi.com/technical-support/packages/</a>

| PACKAGE | OUTLINE / LAND PATTERN | THERMAL CHARACTERISTICS  |

|---------|------------------------|--------------------------|

| SOT-25  | SOT-25 PKG             | SOT-25 Power Dissipation |

| USP-6C  | USP-6C PKG             | USP-6C Power Dissipation |

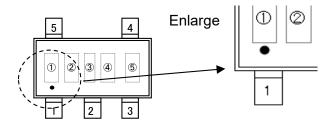

## ■ MARKING RULE

### ●SOT-25 / USP-6C

(\*) SOT-25 has a dot mark, which is printed under MARK ① (refer to drawings below).

### ●SOT-25 (Under dot)

### ●USP-6C

123 represents products series, products type, Oscillation Frequency

| MARK |   |   | SERIES | TYPE | OSCILLATION | I PRODUCT SERIES |

|------|---|---|--------|------|-------------|------------------|

| 1    | 2 | 3 |        |      | FREQUENCY   |                  |

| L    | 4 | 1 | XD9263 | С    | D           | XD9263C75D**-Q   |

| L    | 4 | 2 | XD9263 | D    | D           | XD9263D75D**-Q   |

| L    | 4 | 3 | XD9264 | С    | D           | XD9264C75D**-Q   |

| L    | 4 | 4 | XD9264 | D    | D           | XD9264D75D**-Q   |

4,5 represents production lot number

$01\sim09$ ,  $0A\sim0Z$ ,  $11\sim9Z$ ,  $A1\simA9$ ,  $AA\simAZ$ ,  $B1\simZZ$  in order.

(G, I, J, O, Q, W excluded)

<sup>\*</sup> No character inversion used.

- 1. The product and product specifications contained herein are subject to change without notice to improve performance characteristics. Consult us, or our representatives before use, to confirm that the information in this datasheet is up to date.

- 2. The information in this datasheet is intended to illustrate the operation and characteristics of our products. We neither make warranties or representations with respect to the accuracy or completeness of the information contained in this datasheet nor grant any license to any intellectual property rights of ours or any third party concerning with the information in this datasheet.

- Applicable export control laws and regulations should be complied and the procedures required by such laws and regulations should also be followed, when the product or any information contained in this datasheet is exported.

- 4. The product is neither intended nor warranted for use in equipment of systems which require extremely high levels of quality and/or reliability and/or a malfunction or failure which may cause loss of human life, bodily injury, serious property damage including but not limited to devices or equipment used in 1) nuclear facilities, 2) aerospace industry, 3) medical facilities, 4) automobile industry and other transportation industry and 5) safety devices and safety equipment to control combustions and explosions, excluding when specified for in-vehicle use or other uses.

- Do not use the product for in-vehicle use or other uses unless agreed by us in writing in advance.

- 5. Although we make continuous efforts to improve the quality and reliability of our products; nevertheless Semiconductors are likely to fail with a certain probability. So in order to prevent personal injury and/or property damage resulting from such failure, customers are required to incorporate adequate safety measures in their designs, such as system fail safes, redundancy and fire prevention features.

- 6. Our products are not designed to be Radiation-resistant.

- 7. Please use the product listed in this datasheet within the specified ranges.

- 8. We assume no responsibility for damage or loss due to abnormal use.

- 9. All rights reserved. No part of this datasheet may be copied or reproduced unless agreed by Torex Semiconductor Ltd in writing in advance.

TOREX SEMICONDUCTOR LTD.